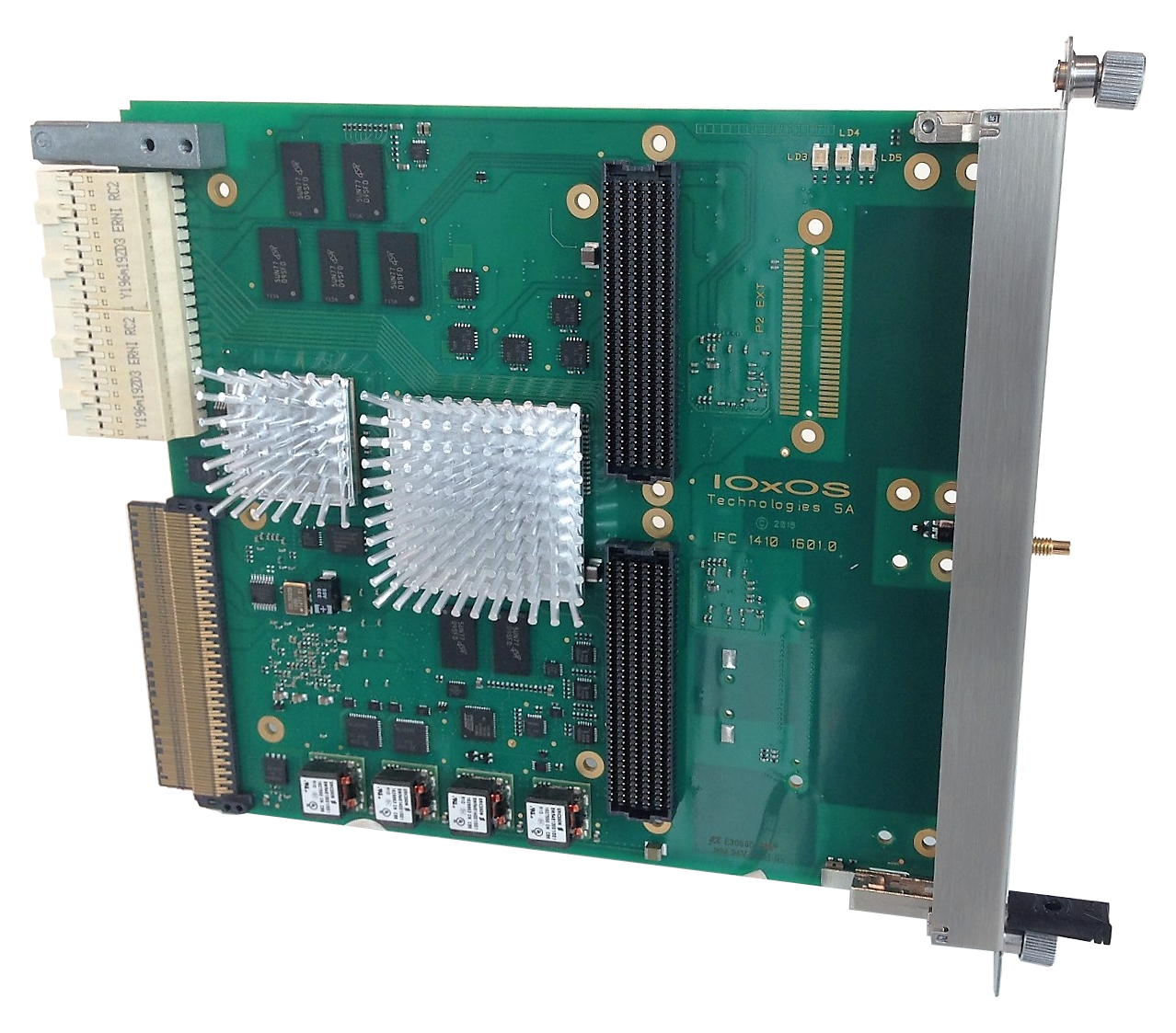

L’ADC_3112 est un module FMC VITA57.1 doté d’ADC haute vitesse 12 bits / 900 (1000) Méch/Sec basse consommation basée sur la dernière génération d’ADC de TI, l’ADS5409. Grâce au support d’entrelacement intégré et à la programmation d’horloge individuelle, deux canaux ADC peuvent être utilisés sur le même canal d’entrée, fournissant un taux d’échantillonnage de 12 bits / 1800 (2000) Géch/Sec.

Les quatre (4) entrées analogiques sont implémentées à travers deux (2) connecteurs haute fréquence SSMC configurables comme différentiel couplé DC ou référencé masse. L’étage de préamplificateur haute vitesse (> 1 GHz), basé sur le dispositif LT6409, fournit des signaux analogiques aux dispositifs ADS5409 et à la fonction de déclenchement analogique.

Le système d’horloge embarquée est implémenté avec un contrôleur LMK04803B entièrement programmable et à haute précision. La source de référence d’horloge est sélectionnable soit à partir de l’entrée SSK CLKREF du panneau avant, soit à partir du bruit de phase ultra-faible embarqué XCO/VCXO, soit à partir du signal LVDS VITA57.1 « CLK0_C2M ».

Pour prendre en charge l’entrelacement de deux dispositifs, et pour fournir une fréquence d’échantillonnage double (1800/2000 Méch/Sec), un retard d’horloge programmable avec une résolution de sous-picoseconde est introduit dans les chemins d’horloge ADC